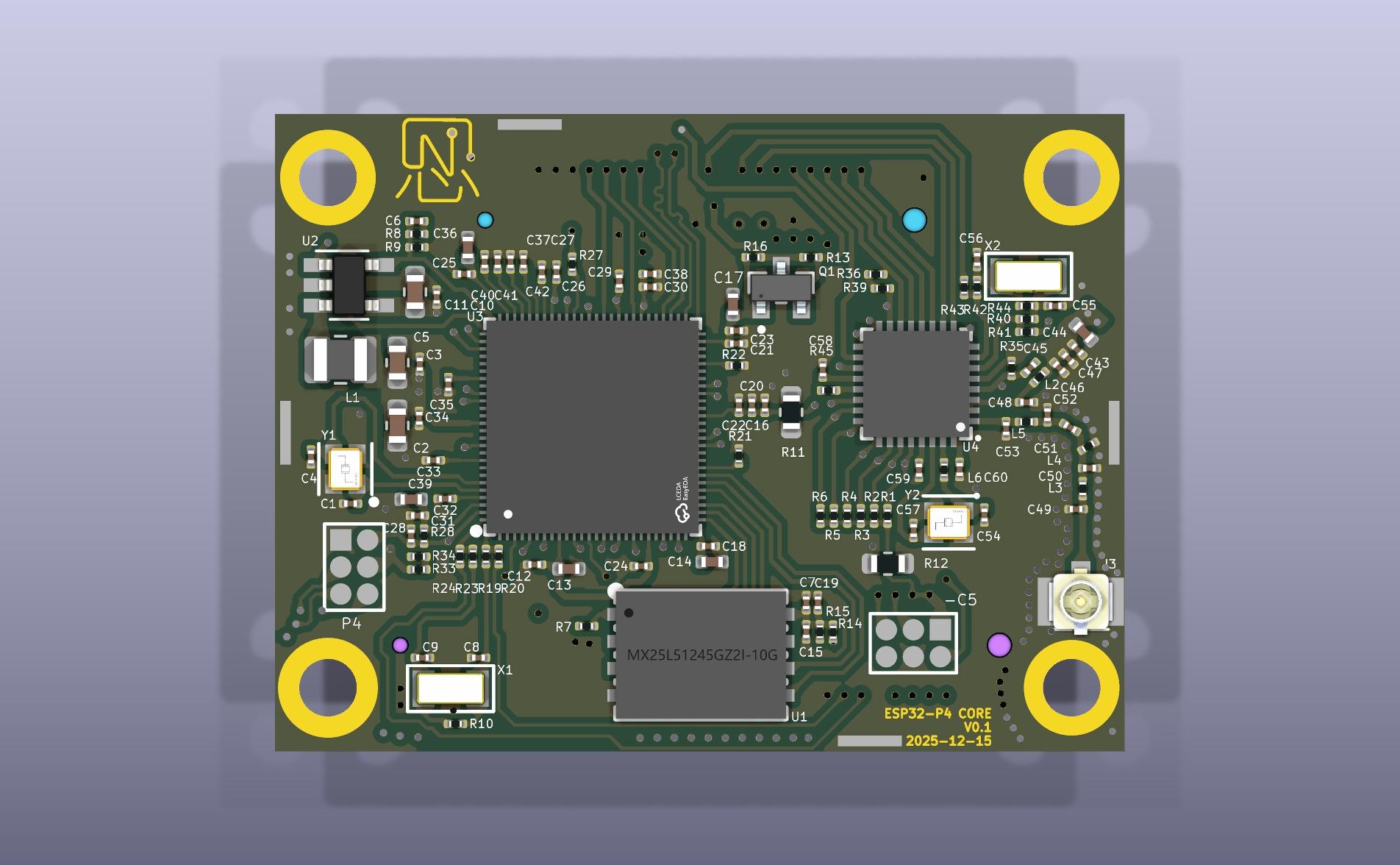

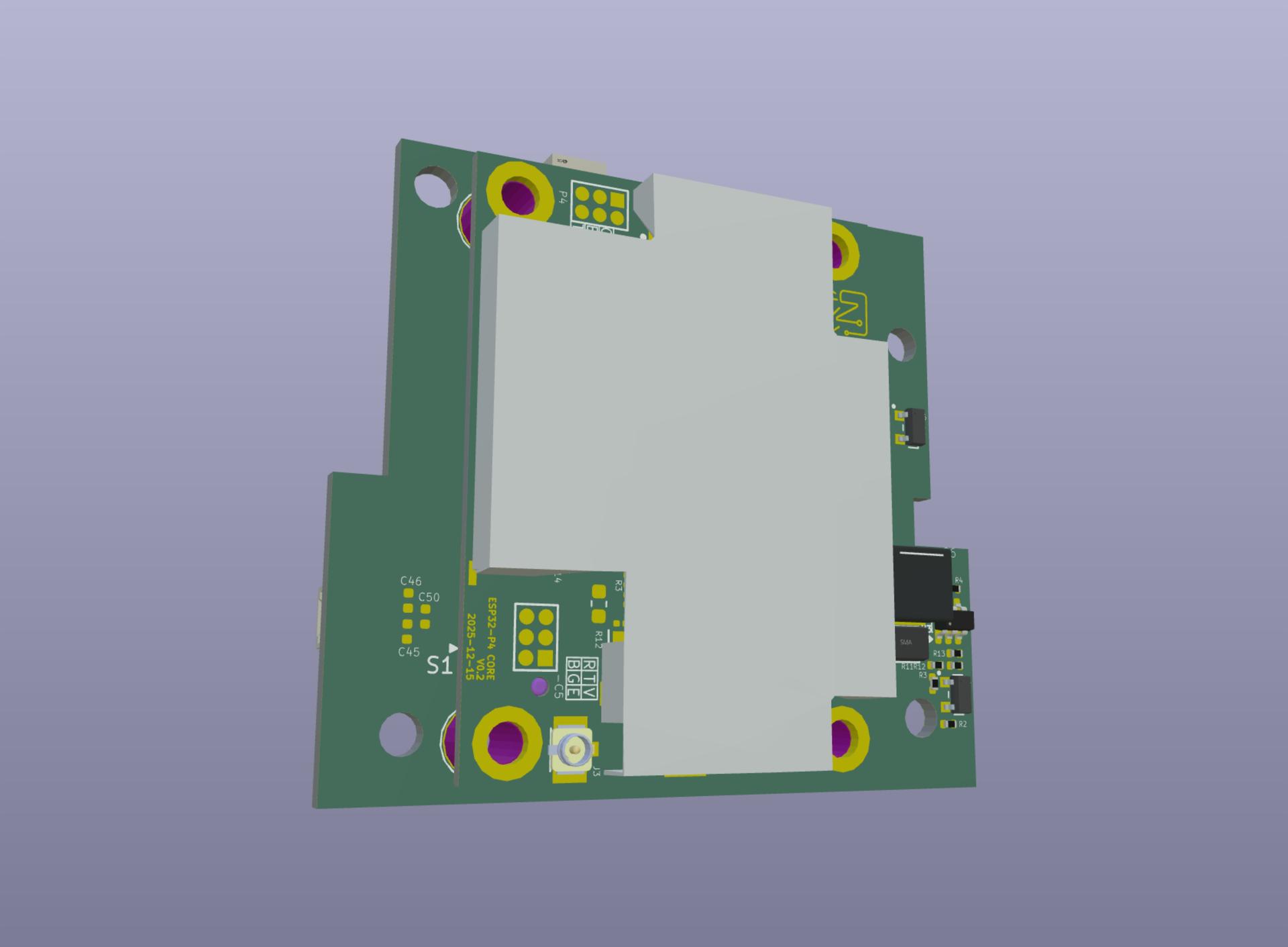

YeaCreate-ESP32-P4-CORE 核心板3D图

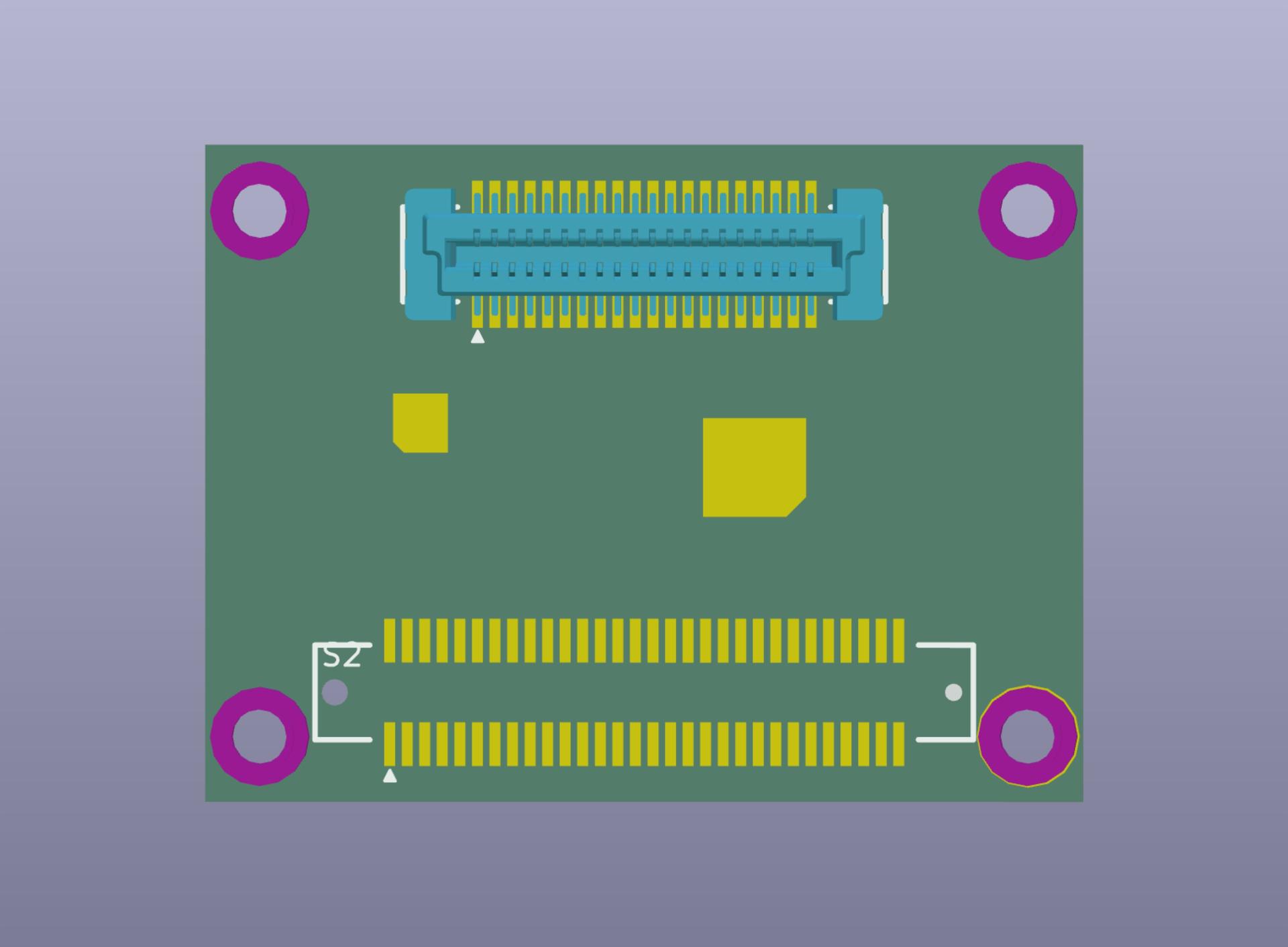

YeaCreate-ESP32-P4-CORE 核心板正面

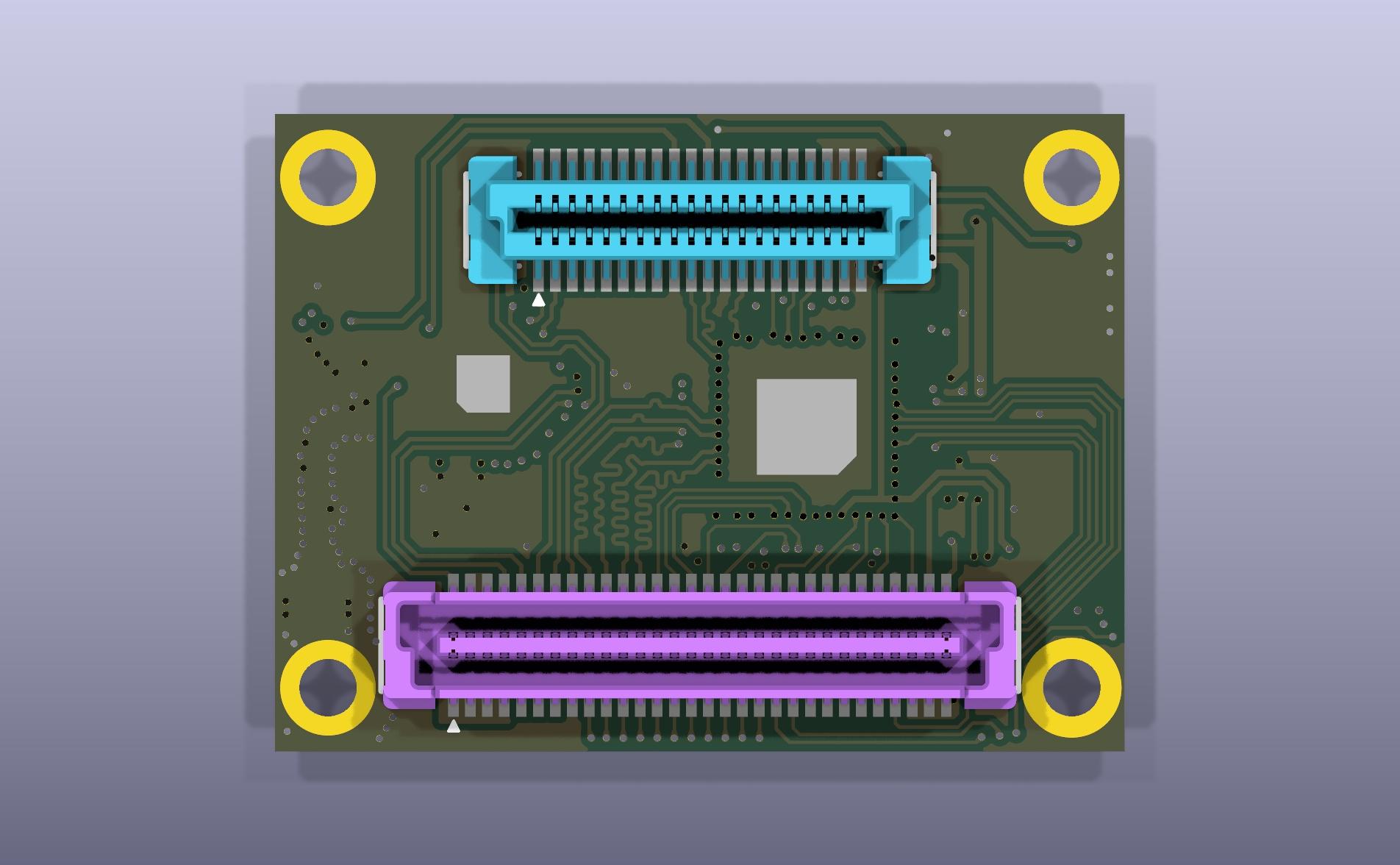

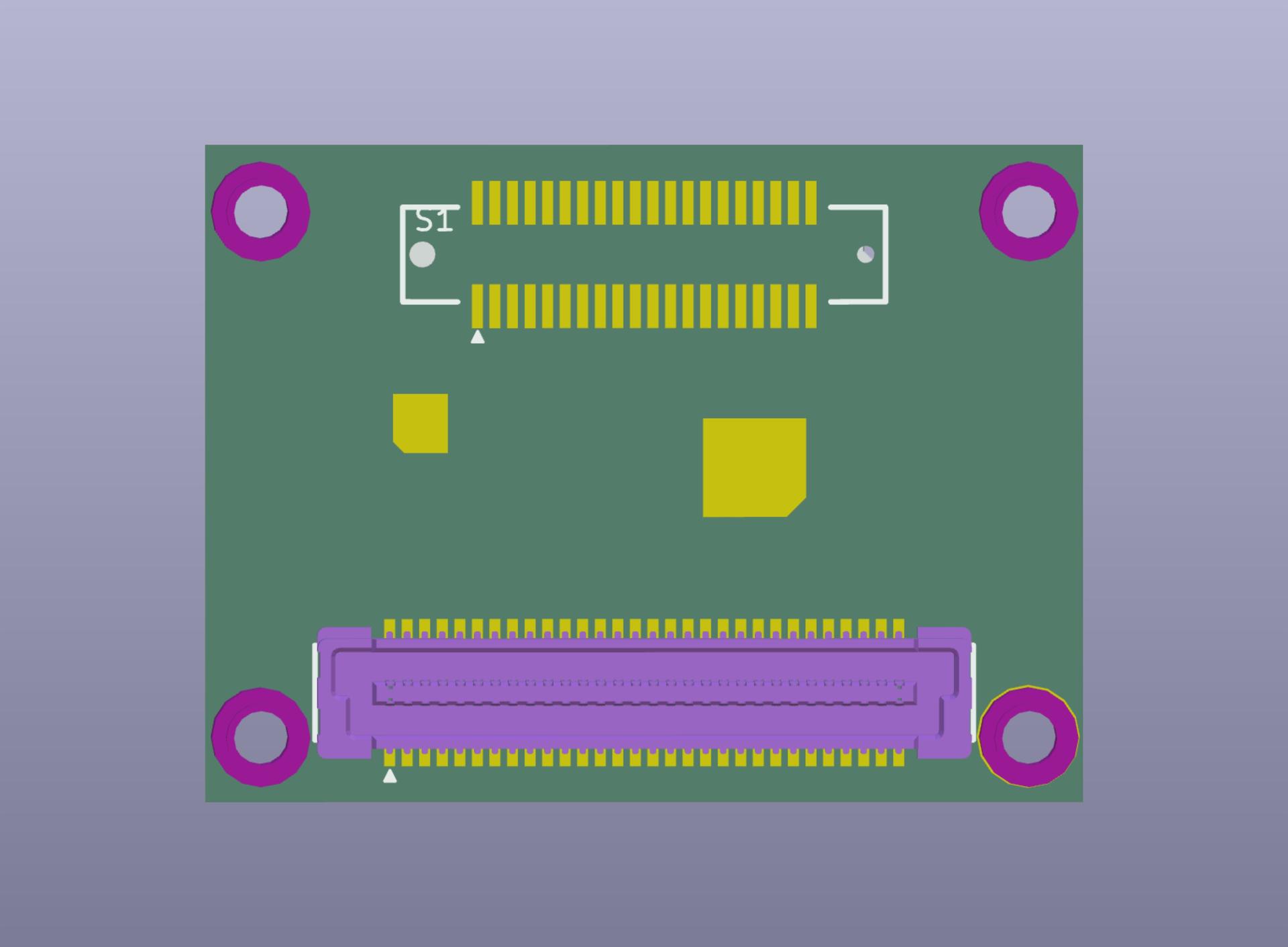

YeaCreate-ESP32-P4-CORE 核心板背面

功能简介

YeaCreate-ESP32-P4-CORE 主板是一款面向新一代智能应用与 AI 开发的高性能核心控制板,集成 ESP32-P4 + ESP32-C6 双芯片架构。其中,ESP32-P4 负责高算力处理与外设控制,ESP32-C6 提供稳定的无线通信能力,使主板在性能与连接性之间实现良好平衡。该主板可选搭配 YeaCreate-ESP32-P4-BODY 使用,组成模块化硬件方案,方便根据项目需求进行功能扩展与产品化设计。

YeaCreate-ESP32-P4-CORE 支持多种外设扩展,包括显示屏、语音输入、音频输出以及 TF 卡存储接口,能够满足图形界面、人机交互、多媒体处理和数据存储等应用需求。其丰富的接口资源和灵活的扩展方式,使开发者可以快速搭建原型并进行功能验证。凭借双芯片协同设计与良好的扩展能力,该主板非常适合用于 AI 推理、智能终端、语音交互设备及其他创新型 AI 项目开发。

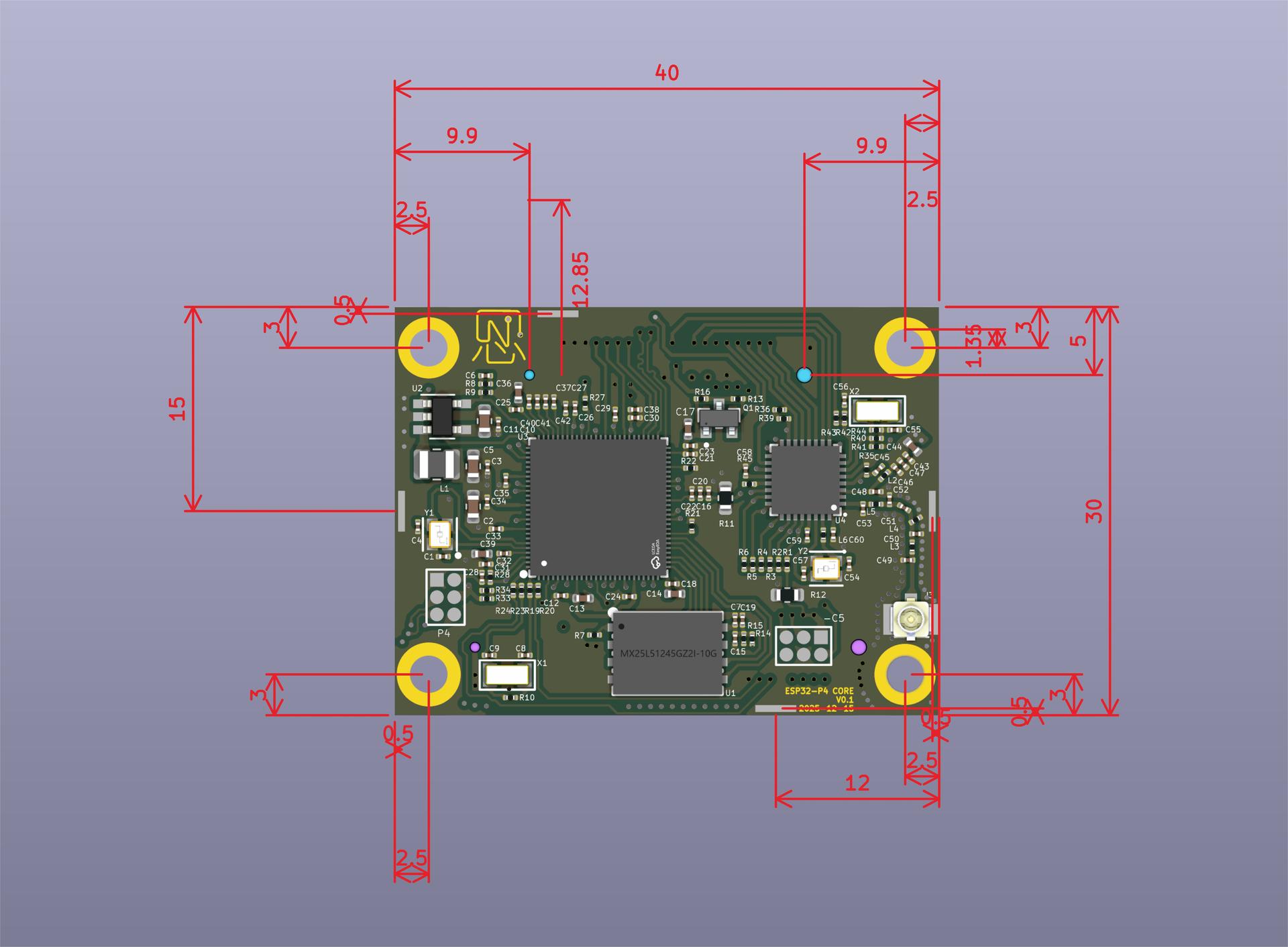

核心板尺寸

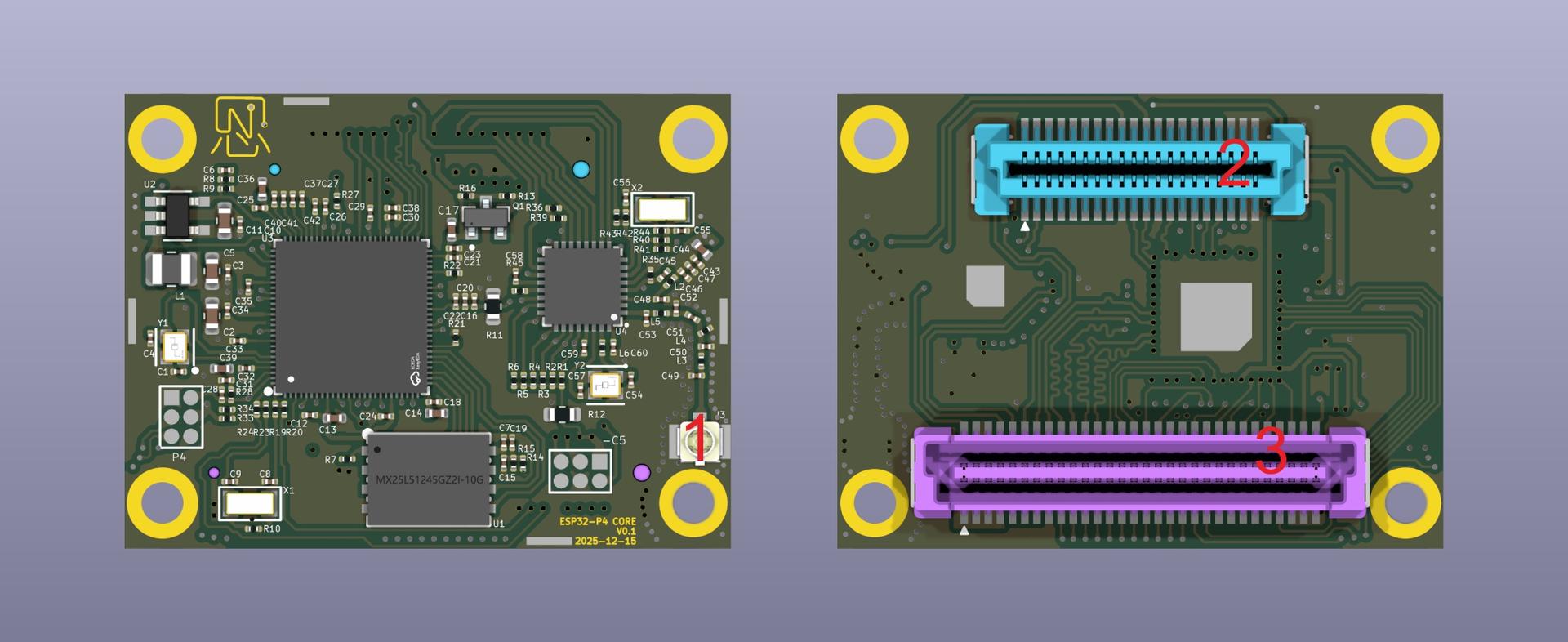

核心板功能

| 编号 |

描述 |

| 1 |

WIFI+BT接口 |

| 2 |

40PIN LGA ESP32-C6功能接口 |

| 3 |

60PIN LGA ESP32-P4 功能接口 |

ESP32-C6 支持 Wi-Fi 6(802.11ax)和 蓝牙 5 (LE),ESP32-P4 是AI 推理与信号处理的芯片,适合对算力要求更高的边缘计算。

ESP32-C6 与 ESP32-P4 可灵活选择整合或独立使用模式,既支持双芯片协同运行,也可分别作为独立控制单元进行开发,互不影响。基于 LGA 接口的设计,使产品在装配方式与系统扩展上具备更高的灵活性。

产品参数

| ESP32-P4 |

主频 360 MHz; 16M PSRAM; 128KB HP ROM; 768KB HP L2MEM; |

| ESP32-C6 |

主频 160 MHz; 320K ROM; 512KB HP SRAM; 16KB LP SRAM; 4MB Flash; |

| WIFI |

2.4 GHz; 支持 IEEE 802.11ax 协议; 完全兼容 IEEE 802.11b/g/n 协议; |

| 蓝牙 |

Bluetooth 5.3; Wi-Fi 与蓝牙共存,共用同一个天线; |

| 电源适配 |

3.6V |

| 外部储存支持 |

TF卡槽 |

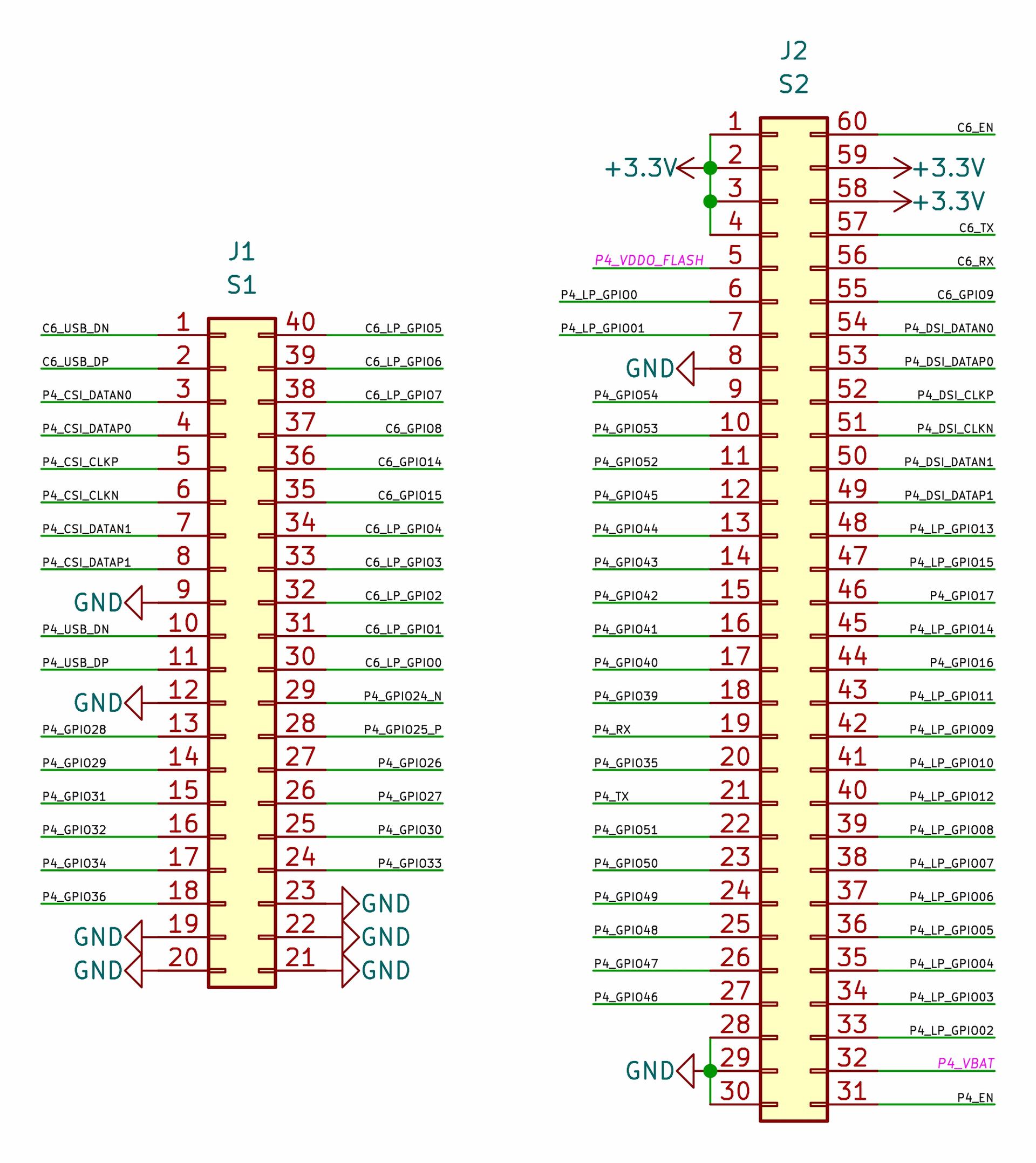

接口定义

- 40PIN RGA (J1 S1)

| 1 |

C6_USB_DN |

40 |

C6_LP_GPIO5 |

| 2 |

C6_USB_DP |

39 |

C6_LP_GPIO6 |

| 3 |

P4_CSI_DATAN0 |

38 |

C6_LP_GPIO7 |

| 4 |

P4_CSI_DATAP0 |

37 |

C6_GPIO8 |

| 5 |

P4_CSI_CLKP |

36 |

C6_GPIO14 |

| 6 |

P4_CSI_CLKN |

35 |

C6_GPIO15 |

| 7 |

P4_CSI_DATAN1 |

34 |

C6_LP_GPIO4 |

| 8 |

P4_CSI_DATAP1 |

33 |

C6_LP_GPIO3 |

| 9 |

GND |

32 |

C6_LP_GPIO2 |

| 10 |

P4_USB_DN |

31 |

C6_LP_GPIO1 |

| 11 |

P4_USB_DP |

30 |

C6_LP_GPIO0 |

| 12 |

GND |

29 |

P4_GPIO24_N |

| 13 |

P4_GPIO28 |

28 |

P4_GPIO25_P |

| 14 |

P4_GPIO29 |

27 |

P4_GPIO26 |

| 15 |

P4_GPIO31 |

26 |

P4_GPIO27 |

| 16 |

P4_GPIO32 |

25 |

P4_GPIO30 |

| 17 |

P4_GPIO34 |

24 |

P4_GPIO33 |

| 18 |

P4_GPIO36 |

23 |

GND |

| 19 |

GND |

22 |

GND |

| 20 |

GND |

21 |

GND |

- 60PIN RGA (J2 S2)

| 1 |

+3.3V |

60 |

C6_EN |

| 2 |

+3.3V |

59 |

+3.3V |

| 3 |

+3.3V |

58 |

+3.3V |

| 4 |

+3.3V |

57 |

C6_TX |

| 5 |

P4_VDDO_FLASH |

56 |

C6_RX |

| 6 |

P4_LP_GPIO0 |

55 |

C6_GPIO9 |

| 7 |

P4_LP_GPIO01 |

54 |

P4_DSI_DATAN0 |

| 8 |

GND |

53 |

P4_DSI_DATAP0 |

| 9 |

P4_GPIO54 |

52 |

P4_DSI_CLKP |

| 10 |

P4_GPIO53 |

51 |

P4_DSI_CLKN |

| 11 |

P4_GPIO52 |

50 |

P4_DSI_DATAN1 |

| 12 |

P4_GPIO45 |

49 |

P4_DSI_DATAP1 |

| 13 |

P4_GPIO44 |

48 |

P4_LP_GPIO13 |

| 14 |

P4_GPIO43 |

47 |

P4_LP_GPIO15 |

| 15 |

P4_GPIO42 |

46 |

P4_GPIO17 |

| 16 |

P4_GPIO41 |

45 |

P4_LP_GPIO14 |

| 17 |

P4_GPIO40 |

44 |

P4_GPIO16 |

| 18 |

P4_GPIO39 |

43 |

P4_LP_GPIO11 |

| 19 |

P4_RX |

42 |

P4_LP_GPIO09 |

| 20 |

P4_GPIO35 |

41 |

P4_LP_GPIO10 |

| 21 |

P4_TX |

40 |

P4_LP_GPIO12 |

| 22 |

P4_GPIO51 |

39 |

P4_LP_GPIO08 |

| 23 |

P4_GPIO50 |

38 |

P4_LP_GPIO07 |

| 24 |

P4_GPIO49 |

37 |

P4_LP_GPIO06 |

| 25 |

P4_GPIO48 |

36 |

P4_LP_GPIO05 |

| 26 |

P4_GPIO47 |

35 |

P4_LP_GPIO04 |

| 27 |

P4_GPIO46 |

34 |

P4_LP_GPIO03 |

| 28 |

GND |

33 |

P4_LP_GPIO02 |

| 29 |

GND |

32 |

P4_VBAT |

| 30 |

GND |

31 |

P4_EN |

核心板配套

该系统采用 核心板 + 核心板 的模块化设计思路,YeaCreate-ESP32-P4-CORE 作为核心计算单元,通过 LGA 接口与核心板进行可靠连接。核心板主要负责电源管理、接口扩展与功能外设集成,可根据不同应用场景进行定制与组合。

在保持核心板通用性的同时,核心板可灵活扩展显示、音频、存储、通信及各类传感器接口,使整套方案在功能配置、装配方式及产品形态上具备更高的可扩展性与适配性,适用于 AI、物联网及嵌入式应用的快速开发与量产部署。